djMEMC Support For Large SIMMs

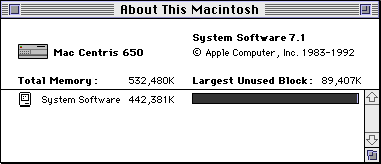

The djMEMC memory controller is used in the 68k Macintosh models Centris and Quadra 610, 650, and 800. These machines, by default, can only use 32MB RAM SIMMs, although some 128MB SIMMs are recognized as 64MB. This is a description of a small ROM modification that will enable the use of 128MB (and likely 64MB) RAM SIMMs, increasing the maximum memory of these machines to 260MB for the 610, and 520MB for the 650 and 800.

In order to modify the ROM on these machines, a ROM SIMM slot is required. At least some models of the Centris 610 have a ROM SIMM slot with a ROM SIMM populated from the factory. Most of these machines do not have a ROM slot, and instead only have solder pads for one.

Doug Brown has developed a ROM SIMM with flash chips on it, which can be used to run modified ROM images.

The development of this modification used a Centris 610 with a ROM slot stock, and Doug's ROM SIMM.

The Centris 650 uses the identical ROM as the Centris 610, so the ROM image below can be used unmodified.

Files:

c610+bigmem+nocrc+noramtest.bin ROM image supporting 128MB SIMMs, with both ROM checksum and RAM tests disabled.

Discussion:

The most recent testing versions, worklog, and discussions can be found in this thread of the mac68k.info forums.

Technical Description:

As I understand it, the djMEMC memory controller is capable of using 64MB per bank, with larger SIMMs using 2 contiguous banks per slot. The Quadra 605 uses a djMEMC derivative, and is capable of using 128MB SIMMs.

On boot, the system ROM determines the size of available RAM. When doing so, it puts the djMEMC into a mode that only addresses 32MB/bank. This modification simply switches the djMEMC mode from 32MB/bank to 64MB/bank. This means that with the modification, RAM SIMM sizes smaller than 64MB/bank may not be detected properly. The solution would be to run through the RAM detection code twice, once in each mode. However, that hasn't bee implemented yet.

The change to the RAM sizing code is:

A0168 223C 0000 0100 Move.L #$100, D1Changing that to:

A0168 223C 0000 0000 Move.L #0, D1RAM Test

When the system cold boots (first powers on), it performs a memory test. This test was pretty quick for the small values of memory, but with the sizes of memory this modification is intended for, the RAM test can take a long time.

There are 2 memory test functions located at 0x477D8 and 0x478F0 in the IIsi ROM. Both functions return via JMP (A6). To disable the memory tests, I've overwritten the starts of these functions with opcode 0x4ED6, which is JMP (A6).

ROM Checksum

The first 4 bytes of the ROM contain a checksum of the entire image. It is advantageous for us to disable the checksum validation for a couple reasons: it makes development easier, it makes it easier for people to make their own changes (tweaking icons, sounds, values), and some Daystar accelerators key off the ROM checksum to alter their behavior. Being able to set the ROM checksum to arbitrary values to alter the behavior of these peripherals can be useful.

The call to validate the checksum is here:

472B8 3E3C 0001 L496: Move $1, D7 472BC 4DFA 0006 Lea.L DT132, A6 ; load address of the next instruction into A6, to be used as a return vector 472C0 4EFA 0586 Jmp L497 ; L497 here is StartUpROMTest 472C4 4A86 DT132: Tst.L D6 ; Check the return value 472C6 6600 2630 BNE L470 ; L470 is Error1Handler, aka bad chimes. 472CA 4247 Clr D7So replacing 472BC through 472C9 with NOP (4E71) disables both the call to check ROM and the test of the return result. Updated November 28 2012